6400 Multiplexor

Reference Manual

Berkeley Computer Center

# REFERENCE MANUAL FOR THE BERKELEY COMPUTER CENTER MULTIPLEXOR

## CONTENTS

- 1 Introduction

- 2.0 General Programmers Interface

- 3.0 Multiplexer Design

- 3.1 Module Interface

- 3.2 Data Flow

- 3.3 Addressing System

- 4.0 Mechanical Construction

- 5.0 Card Notation

- 6.0 Cage Layouts

# 7.0 Initial Address Allocation

#### Introduction

A large number of teletype units and other devices will be attached to the CDC 6400 computer. The basic interface to the peripheral computer of the 6400 is expensive, but has a high capacity. The multiplexor will have a single 6400 channel interface and connect to a large number of devices. It is being designed on a modular basis, so that it is easy to increase the number of slow external devices as needed. This design approach will make it more expensive but more versatile than a custom designed unit, or one using a central shared store.

The entire multiplexor hardware system has component parts as follows:

- 1) Level changing circuits to change the external device levels to those of the Fairchild logic. This also includes local and safety controls which may be considered part of the device.

- 2) Serialiser Units. These take the incoming signals and convert them to parallel form. They also provide enough bufferage to ensure that a 2 ms. response will suffice. The exact form of a serialiser is tailored to the device that is using it, but it is connected by a regular interface to the central multiplexor unit.

- 3) Central Multiplex Unit. This will determine the highest priority transfers needed and transfer between the appropriate serialiser unit and central buffer registers. Flags will indicate to the computer program when the central buffers need emptying or filling, and periodic attention by the peripheral processor program will ensure this is done.

The structure of the device from a programming point of view is that of a store of up to 512 registers to which information can be read or written, together with a ready system to avoid unnecessary seeking instructions. Most devices will have a control bit so that the program can selectively ignore their ready signals.

An entire channel and peripheral processor are expected to be assigned to the multiplexor. If other synchronisers are attached to the same channel, the multiplexor must be <u>last</u> as it does not relay signals. The multiplexor responds only to the following function codes and will be disconnected by an inactive pulse from the programme.

The functions to which the multiplexor responds are:

7774 Read up to three words from the multiplexor.

7775 Word l is control information.

2 is address in the multiplexor of device selected, the least significant bits giving the address.

3 is data from device selected.

7763

7773

7767

Word 1 is the device address in the multiplexor.

Word 2 is data for the device.

7777 Exchange data with the multiplexor. (Mainly intended for test purposes.)

Word 1 is the device address in the multiplexor.

Word 2 is data for the device.

The device is read from and filled in one operation. The data read from the device will be read eventually by 7774. The program will have to await write buffer empty, then read ignoring associated address.

As each function is completed an inactive pulse must be sent to the multiplexor to release it. See CDC input output specifications.

When reading either one, two, or three words may be read from the multiplexor. The act of reading the second word the multiplexor

buffer if the read buffer was full. No more than three words should be read. The control word ( first word read ) has bits which indicate:

(a) whether there is valid data to be read( $2^0$ =1 if ready)

- (b) whether the write buffer is free  $(2^{l}=1 \text{ if busy})$

- (c) whether the valid data came from a high writing address  $(2^2=1)$

- NOTE: Other bits of the control word may be specified later, hence their values should not be assumed.

# TELETYPE MODULES (8 Bit Codes)

Х<sub>11</sub>....Х<sub>0</sub> Data read from the device is where X \_\_\_\_ if ready was bet (i.e. unless exchange function has just been used.)  $X_0 - X_7 = character bits d_7 - d_0$ . FS  $X_{\bullet} = 0$  unless the line is broken **X** = one if character emptying was overdue, or if the device was unsynchronised.

If the line is broken characters consisting of ones will appear until the input is disabled. ( approx. one character each 95 milliseconds)

The read address is  $\mathcal{N}$ . The device may be ignored by sending a word with  $X_{11} = 1$  to address n. After master clear the device will be ignored. The output may be mixed with the input data by sending a word with  $X_{10} = 1$  ton.

The write address is n+256. The output to be sent is X - X where

$X_0 = 0$ X, \_1  $X_2 - X_3 = bits of character (order to be determined)$ TSAME as import A HES PARCO  $X_{10} = 0$  $X_{12} = 1$

NOTE: a single ready is generated for each character output, and no disable is (A) needed as no readies are generated when no characters are being output.

B For output, if power on for at least 1/10 second then deadstart master clear, no readies will be generated.

#### OVERALL DESIGN OF THE MULTIPLEXOR

The central part of the multiplexor communicates with a channel and the serialisers. There are buffers for data and an address from a PPU. is When hoaded from the PPU the data buffer serially emptied to the specified address. When data is emptied from one of the serialisers into the read buffer, the PPU can then read it. The high speed logic of the multiplexor is slaved to and directly controlled by a PPU and will simply gate data in and out along 12 parallel buses. It will also set 3 control flip flops namely: Read buffer empty, Write buffer full, and exchange needed.

The serial control logic will interpret these three control flip flops and serially fills or empties the appropriate buffers.

The logic has been split into six data routing cards each holding 2 bits of all the parallel registers and all identical, and are card for the high speed logic and one for the slow speed serial logic.

#### Nodule Interface

X,

Bach module communicates with the control part of the multiplexor by five signals.

$\overline{Y}_{i}$   $\overline{Y}_{i}$  is inverted and gated with  $X_{i}$  to form an <u>address</u> <u>selection</u> signal g.

outbus. This is the 'ready' signal and the serial output. The design of the module be such that it is set to 1 only when selected. **Ser** This is the input serial signal. It is only other than 1 when **g** is present. It is used to load any needed shift registers from the central multiplexor. It is sampled at the trailing edge of sh. ch This is a shift control pulse. The back edge is used for shifting. **Ser** and sh must be gated by **g** so that other module signals are ignored.

## Data Flow and Operation

There are five 12 bit registers.

- l Catch register CR. This is used to extend a 25 nanosecond pulse from the PPU.

- 2 A peripheal address register PA. This is loaded from CR and can be connected to the address decoder. Only 9 bits are likely to be used.

- 3 A data shift register PD. This holds data from the peripheal. It is loaded in parallel and emptied serially, which also clears it.

- A serial to parallel data register SD. This is loaded serially and copied in parallel to the PPU. This is also used to generate a mask and serially gate into the generated address register.

- 5 An address generator register. This can be gated to the decoder, together with a mask. It is set one digit a time -- however it is not a shift register.

3.1

There is a two-way gate to the address decoder. Either PA or GA and SD as a mask are gated to the decoder. There is a three-way gate connected to the cable-driver circuits which send data to the PPU. First, control data; second, generated address; third, SD.

. •

#### OMOTEN SKETCH

une.

waveforms on

Basic system takes an 8 bit address and generates if 16 X and 16 Y serialistr belection wires. EachAunit takes a single X and a single Y to that select unit.

To select a unit which is ready we use the same decoding tree as follows: A typical unit is selected by  $\mathbf{a}_0 \ \mathbf{a}_1 \ \mathbf{a}_7$ . If we replace  $\mathbf{a}_1$  by  $\mathbf{b}_1$  the decoder tree has now 16 independent inputs.

Set  $a_i = 1$  and  $b_i = 1$  All units are selected and the output will be the 'or' of all read fies.

Now set  $a_0 = 0$   $a_1 - a_7 = 1$  and  $b_1 = 1$

We have generated the 'or' of  $\frac{1}{2}$  the readies and this will indicate if any ready has  $a_0 = 0$  as the most significant bit. If there is a =0 and  $b_0 > 1$ , if there is no selected ready set  $a_0 > 1 & b_0 > 0$ ready set  $a_0$  and  $a_1$  accordingly and now set  $a_1 = 0$ . This will tell us if  $a_1$  can be 0 for a ready signal.

Thus we can obtain the address digits one at a time. The ready with the lowest address number will thus be selected.

This simple system has the drawback that 256 elements are switched simultaneously, giving about an amp of pulse current. This may gril trigger or affect the circuits with their low noise margin.

To alleviate the possible trouble we arrange

- 1) local amplifiers so that most of the pulse current is local.

- 2) arrange that Y signals are inverted. This needs a number of extra inverters,

but the currents remain roughly balanced.

Similarly the two control signals (serial input and shift) are distributed to all units. These are balanced by sending one -ve to

3.3 (con't)

each unit and using one inverter to obtain true signal. The rclay boards are used for local amplification of the gating and other signals. They also mix the serial outputs and gate them -- an extra precaution against large circulating current loops. They also gate ser and sh, to reduce the chance of noise generation.

### Address Decoding Layout

There are three registers from which addresses are derived.

- 1) PA This is set by the PPU under the control of a program

- 2) GA This is generated in response to a ready signal

- 3) SD This is used in the generation of an address to supply a bi sequence as described above.

These are gated on the 6 data routing boards and sent to 3 address decoder boards. The address decoding boards each do an initial decoding and produce 8 powerful semidecoded signals. Each relay board was 10 of these signals and decodes them further to produce 8 selection signals. Pairs of these selection signals are decoded finally on the 16 serialiser addresses controlled by the relay board.

Buitable back wirring will enable.

| 2 | decoder | bounds | lò | senria | 256  | addrenes. |

|---|---------|--------|----|--------|------|-----------|

| Э |         |        |    |        | 512  |           |

| 6 |         |        |    |        | 1024 |           |

|   |         |        |    |        |      |           |

with no extra stages of decording needed. The current back wiring is for 512 addresses.

## Mechanical Construction and General Layout.

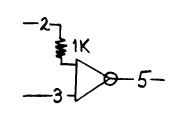

The greater part of the system will be constructed with Fairchild elements 900, 914, and 923. These are integrated RTL circuits. Cards.

A group of such elements is mounted on a <u>card</u> or board. Each card has 60 positions, six rows of 10 numbered from 10 - 69 in which the elements -- or other components may be mounted. The card has a connector of 44 pins of which 32 are used for logic signals and the others used for power and grounding. In addition up to 8 test points may be provided as a maintainance aid.

### Cages.

Each cage has 27 positions numbered 1-27 in which cards may be inserted. the spacing is  $l\frac{1}{2}$  times the minimum width to give ample room for components on the cards.

## Rack

A rack will contain up to 8 logic cages two cage spaces being used for power supplies.

#### Rack Layout

|   | power repplies      | ]               |

|---|---------------------|-----------------|

| ſ | A central control   |                 |

|   | B liketype modulos. |                 |

|   | د                   | -PIU<br>cables. |

|   |                     |                 |

|   |                     | -               |

|   |                     |                 |

|   |                     | -               |

| 1 |                     | 4               |

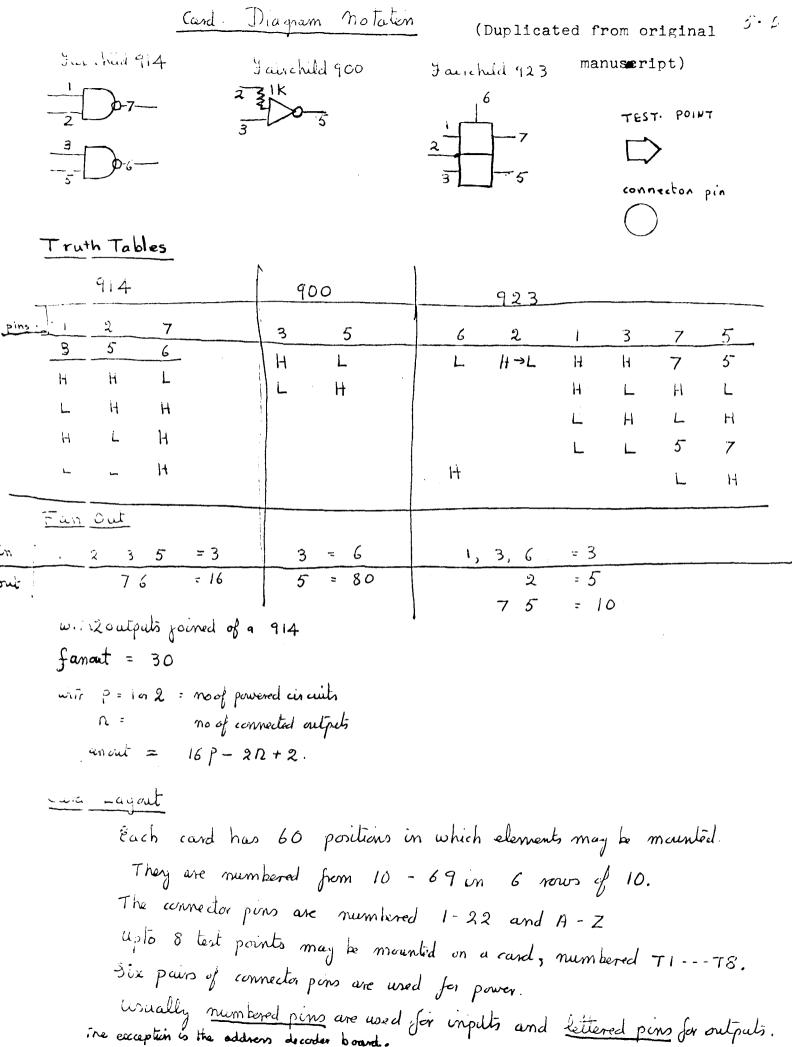

Fairchild 914

Fairchild 900

| T   |     | 4   |              | <br>  | <u> 10 – – – – – – – – – – – – – – – – – – </u> |   | 6            |     | ⊪ۇ⊽سكسلۇ | an maan<br><b>D</b> |        |        | n erset state († 77 e |

|-----|-----|-----|--------------|-------|-------------------------------------------------|---|--------------|-----|----------|---------------------|--------|--------|-----------------------|

| PIN | 1   | 2   | 1            | <br>5 | 2                                               |   |              | 2   |          | 3                   |        |        | majasan mita wa m     |

|     | (3) | (5) | (6)          | _     |                                                 |   |              |     |          |                     |        |        |                       |

|     | Н   | H   | $\mathbf{L}$ | Н     | L                                               |   | $\mathbf{L}$ | H→L | Н        |                     | •      | 5      |                       |

|     | L   | H   | Н            | L     | Н                                               |   |              |     |          | $\mathbb{L}$        | H      | L      |                       |

|     | Н   | Ŀ   | Н            |       |                                                 | 1 |              |     | L        | H                   | և<br>հ | H<br>7 |                       |

|     | Г   | L   | Н            |       |                                                 |   | Н            |     | L        | Ч                   | ン<br>し | H      |                       |

|     |     |     |              |       |                                                 |   |              |     |          |                     | _      |        |                       |

|     |     |     |              | 1     |                                                 | } |              |     |          |                     |        |        |                       |

Fanout:

| IN. | 1,2,3,5 = 3 | 3 <b>=</b> 6  | 1,3,6 = 3        |

|-----|-------------|---------------|------------------|

| OUT | 7,6 = 16    | 5 <b>=</b> 80 | 2 = 5 ; 7,5 = 10 |

with 2 outputs joined of a 914

ranout = 30

with p = 1 or 2 = no. of powered circuits

n = no. of connected outputs

fanout = 16 P-2n+2

# Card Layout

Each card has 60 positions in which elements may be maintained. They are numbered from 10 - 69 in 6 rows of 10.

The connector pins are numbered 1-22 and A-Z.Upto 8 test points may be mounted on a card, numbered Tl....T8. Six pairs of connector pins are used for power. Usually <u>numbered pins</u> are used for inputs and <u>lettered pins</u> for outputs. The exception is the address decoder board.

| Physical Locations | Addresses       |                                                            |  |  |  |  |  |

|--------------------|-----------------|------------------------------------------------------------|--|--|--|--|--|

|                    | read write      | devices                                                    |  |  |  |  |  |

| Cage B.            | 240-255 496-511 | 16 teletypes.                                              |  |  |  |  |  |

| Cage C.            | 208-233 464-479 | 16 1050's                                                  |  |  |  |  |  |

| Cage D.            | 144-151 400-407 | 8 fast lines read. 8 fast<br>lines write (2400 bits/sec.). |  |  |  |  |  |

· ·

----

EXTRA PAGES FROM MUX MANUAL

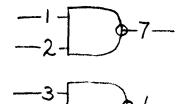

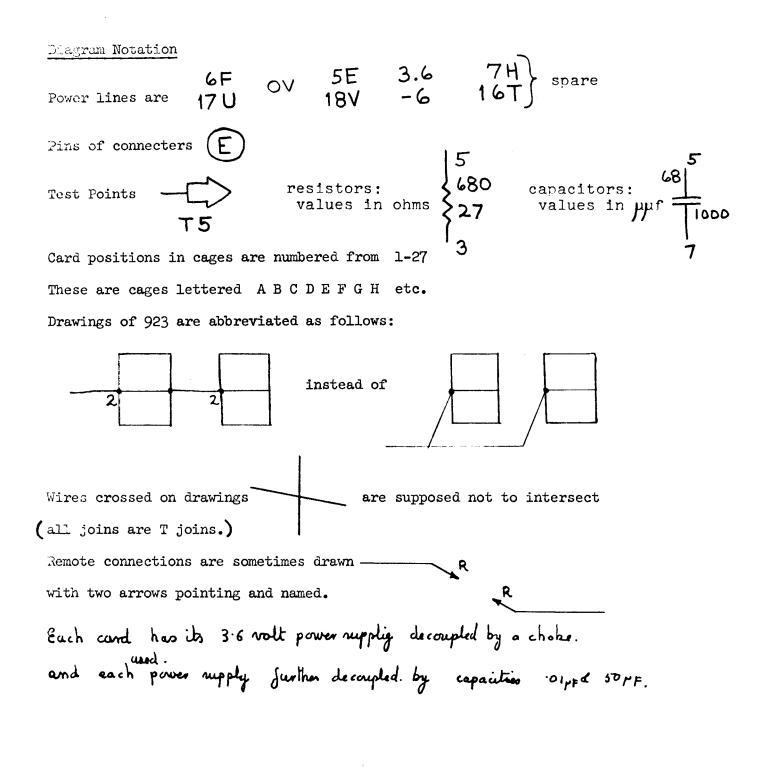

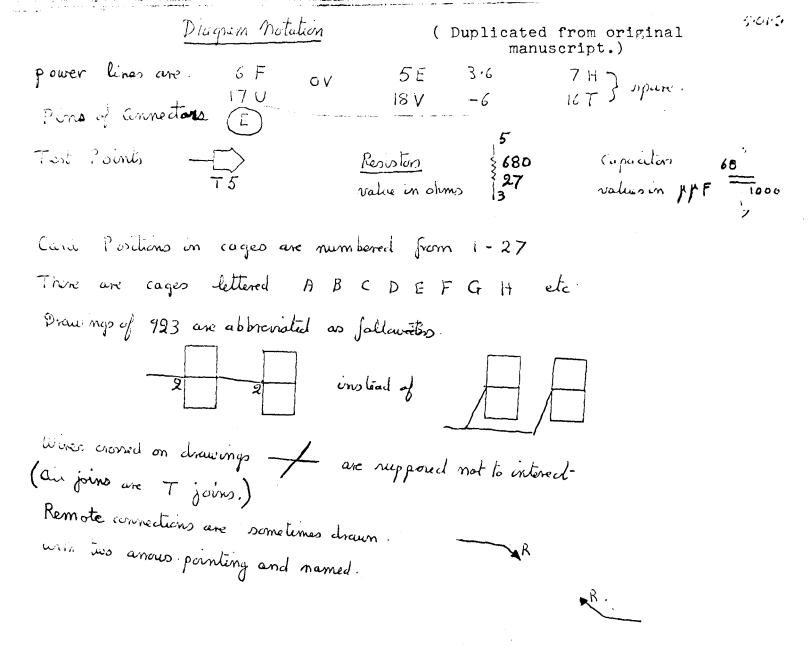

## Diagram Notation

Power lines are

Pins of connecters

Test Points

Card positions in cages are numbered from 1-27These are cages lettered A B C D E F G H etc. Drawings of 923 are abbreviated as follows:

#### instead of

Wires crossed on drawings are supposed not to intersect all joins are T joins. Remote connections are sometimes drawn with two arrows pointing and named.

Each card has its 3.6 volt power supply decoupled by a choke. and each power supply further decoupled by capacities .014= & 504=.

\_\_\_\_